Physical Channels for 5G NR

Introduction

In the context of 5G (fifth generation) cellular networks, physical channels are communication channels that operate at the physical layer of the network architecture. These channels are responsible for carrying the actual user data and control information between the user equipment (UE) and the base station (NodeB or gNB in 5G).

Here are the main types of 5G physical channels on the base station:

- Physical Downlink Shared Channel (PDSCH)

Provides a shared data channel for transmitting user data, such as video, audio, or other application data from base station to user equipment. - Physical Uplink Shared Channel (PUSCH)

Carries user data from the UE to the base station, enabling UEs to transmit their data to the network. - Physical Downlink Control Channel (PDCCH)

Carries control information that is used to manage the transmission on the physical channels, such as resource allocation, power control commands, and scheduling information. - Physical Uplink Control Channel (PUCCH)

Used for transmitting uplink control information from the user equipment (UE) to the base station The PUCCH carries information such as acknowledgments (ACK/NACK) for received data, scheduling requests, and other control signals. - Physical Random Access Channel (PRACH)

The PRACH serves as the physical channel through which UEs can initiate communication with the network when they do not have a dedicated radio resource, and is essential for initiating communication between a user equipment (UE) and a base station. - Physical Broadcast Channel (PBCH)

The primary function of the PBCH is to broadcast the parameters from the base station to UEs to synchronize with the cell and establish initial communication with the network.

These physical channels are essential components of the 5G air interface, facilitating the exchange of information between the network infrastructure and the user devices for efficient and reliable communication.

AccelerComm licences the components of the 5G Physical Layer channels as 3GPP-compliant IP modules which accelerate processing for optimal power and performance. The modules are designed for ASIC and FPGA implementation, and can be configured and controlled by the physical layer software. This enables customers to integrate optimised channel accelerators into their own physical layer implementations.

Forward Error Correction Accelerators

LDPC

Our high throughput LDPC encoding and decoding IP modules for the 3GPP 5G New Radio uplink and downlink data channel include the entire processing chain, to provide quick and easy integration.

The innovative patented LDPC algorithm was designed specifically for 5G, and complete configurability enables flexible 5G LDPC decoders with high throughput, low latency, and high hardware efficiency without introducing error floors.

LDPC Features

- Patented high performance implementation

- Complete 3GPP compliant chain

16x latency improvement (to support numerology 4) - Supports full code block and transport block processing

- Open standard software API’s (DPDK) and reference kits

- Delivered in multiple form factors for ASIC, FPGA and Software only

Polar

In 5G, Polar codes are used in various channels, including the control channels like PDCCH and PUCCH. The use of Polar codes in these channels helps improve the reliability and efficiency of communication in the presence of noise and interference.

AccelerComm has developed a unique Polar architecture which enables higher degrees of parallel processing than before. It is easy to integrate, significantly reducing resource and memory usage while delivering excellent BLER performance.

Polar Features

- Patented high performance implementation

- Complete 3GPP compliant chain

- High degrees of parallel processing and scalability

- Superior hardware efficiency and latency reduction

- Delivered in multiple form factors for ASIC, FPGA and Software only

- Configurable decoder list size to best fit the BLER/PPA requirements

Channel Accelerators

PUSCH Decoder

The PUSCH Decoder accelerator integrates the UCI over PUSCH functions, together with demultiplexing, descrambling, and demodulation of the data stream.

This brings its own performance advantages - For instance, a key bottleneck in the Uplink receive chain is often the very high data rate required to pass data to the LDPC decoder as LLRs. By integrating the Demodulator and and passing the data as IQ values, the AccelerComm IP offers an opportunity to reduce this bottleneck by a factor of two.

PUSCH Decoder Features

- Implemented for 3GPP NR specifications and compliant with TS 38.211 and 38.212

- New QAM modulator/demodulator functionality complements existing LDPC and Polar decoding solutions

- Inherits all the benefits from the existing AccelerComm LDPC, Polar decoders

- Support for Uplink Control information (UCI) multiplexed onto the PUSCH

- Improved BLER for UCI control data

- Configurable to different parallelisms specific to each integration

- Targets both FPGA and ASIC implementations

PDSCH Encoder

The PUSCH Encoder accelerator adds scrambling and modulation to the LDPC Transport Block Encoder.

PUSCH Encoder Features

- Implemented for 3GPP NR specifications and compliant with TS 38.211 and 38.212

- New QAM modulator functionality complements existing LDPC coding solutions

- Inherits all the benefits from the existing AccelerComm LDPC encoder

- Configurable to different parallelisms specific to each integration

- Target both FPGA and ASIC implementations

PUSCH Equaliser

The AccelerComm PUSCH Equaliser is an extension to the AccelerComm PUSCH Decoder supporting all the same features but with the additional integrated Equaliser block.

The AccelerComm PUSCH Equaliser includes advanced interference cancellation algorithms and is targeted at improving spectral efficiency in solutions that have multiple antennas. Advanced Equalisation algorithms require significant signal processing requirements and are therefore better implemented as hardware acceleration than in a general purpose CPU.

PUSCH Equaliser Features

- Implemented for 3GPP NR specifications and compliant with TS 38.211 and 38.212

- Can double spectral efficiency dependant on deployment scenario

- Reduces cost per bit and lowers system power

- Integrates advanced equalisation with demodulation, LDPC and polar decoding

- Minimises time to market

- Available for FPGA and ASIC

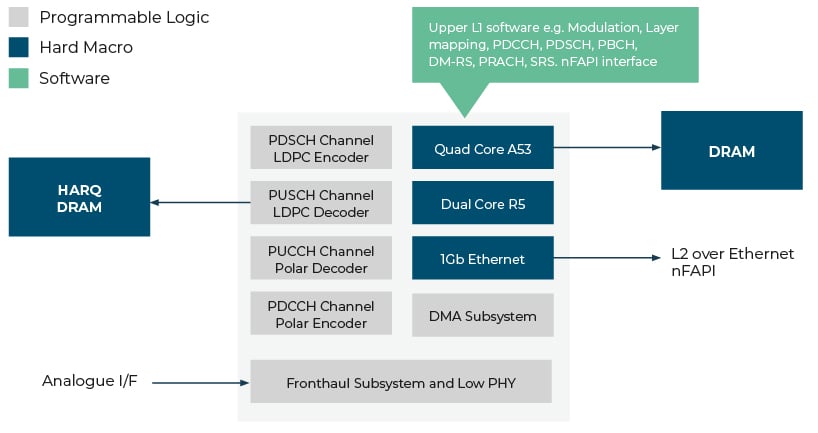

AccelerComm product mix

Below is a diagram showing the integrated components to the Channel IP:

Testimonials

AccelerComm is providing us with Acceleration IP on our Telco Accelerator cards. They are an excellent partner. The one thing I can tell you about AccelerComm, is the high quality of their products. The out of the box experience has always been superb.

Very professionally done, very professional team, easy to work with. They’re great partners.

AccelerComm has been a key partner in providing that flexibility in order to meet the performance requirements we need for our customers.

The relationship has been excellent. Because of the nature of our business, where we customise our solutions very specifically for our customers, there’s been a lot of engineering back and forth between ourselves and AccelerComm. And so quite often, we will need to tailor both their and our solutions to the specific requirements of a given customer.

AccelerComm is a great partner of ours. We deliver together the IP for the FPGAs. They deliver, they support us and create for us opportunities in the market.

We love Rob. B. He is supporting us with both opportunities and technologically. So a great experience and great company to work with.